I'm trying to design an elevator controller in SystemVerilog. The code compiles well but the testbench is completely different when I put it in gtkwave. The controller receives 3 different inputs (one for each of the 3 floors, like buttons of a proper elevator) and passes its output to the elevator engine, which can stay on the same floor, go up or go down by one or two floors.

This is the code for the module:

enum logic [4:0] {fermo, sale, sale2, scende, scende2} motore;

module ascx (input logic x0, x1, x2, clk, reset,

output logic [4:0] y);

enum logic [1:0] {pianoterra, primopiano, secondopiano} piani;

logic [1:0] pianoatt, pianoprox;

always_ff@(posedge clk, posedge reset)

if(reset) pianoatt <= pianoterra;

else pianoatt <= pianoprox;

always_comb begin

if(x1) pianoprox = primopiano;

else if(x0) pianoprox = pianoterra;

else if(x2) pianoprox = secondopiano;

end

always @(*) begin

case(pianoatt)

pianoterra: begin

if(x0) assign y = fermo; /*assign y = 5'b00001;*/

if(x1) assign y = sale; /*assign y = 5'b00010;*/

if(x2) assign y = sale2; /*assign y = 5'b00100;*/

end

primopiano: begin

if(x0) assign y = scende; /*assign y = 5'b01000;*/

if(x1) assign y = fermo; /*assign y = 5'b00001;*/

if(x2) assign y = sale; /*assign y = 5'b00010;*/

end

secondopiano: begin

if(x0) assign y = scende2; /*assign y = 5'b10000;*/

if(x1) assign y = scende; /*assign y = 5'b01000;*/

if(x2) assign y = fermo; /*assign y = 5'b00001;*/

end

default assign y = fermo;

endcase

end

endmodule

Here's the testbench:

module tst_ascx();

logic clk, reset, x0, x1, x2;

logic [4:0] y;

ascx dut(clk, reset, x0, x1, x2, y);

always begin

clk=0; #10;

clk=1; #10;

end

initial begin

$dumpfile("ascx.vcd");

$dumpvars;

reset=1; x0=0; x1=0; x2=0; #10;

reset=0; x0=1; x1=0; x2=0; #10;

x0=0; x1=1; #10;

x1=0; x2=1; #10;

x0=1; x2=0; #10;

x0=0; x2=1; #10;

x1=1; x2=0; #10;

x0=1; x0=0; #10;

end

endmodule

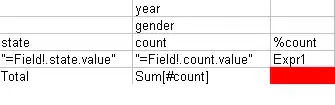

The clock, as shown in the image, is not correct.

The input x0 should not be periodic, it simply represents a button being pressed at some time.

I can't say if for the rest the module is working properly, because of these two problems.