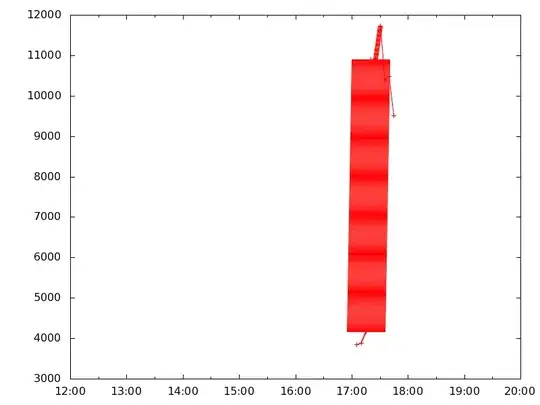

I'm reading a textbook that introduces floating-point architecture based on AVX (for “advanced vector extensions”), below is the pictures of available media registers:

I don't understand why those register needs to be 256-bit (32 bytes), isn't that float data type is 4 bytes and double is 8 bytes, then we can just use normal integer registers suhc as %rdi, %rsi, %r8 etc, those 64-bit registers suffice?