I use the STM32 family of microcontrollers, more specifically the STM32F7 series. Currently I'm investigating the use of general-purpose timers.

About double buffered registers.

Microcontrollers sometimes make use of double-buffered registers. In this way, the software can write to and read from the register without causing troubles. The following figure explains:

buffered register: active register:

-------------- --------------

| REGX_BUF | <-------> | REGX |

-------------- --------------

| |

| |

SOFTWARE HARDWARE

The software interacts Updates to and from the

only with the buffered active register take place

register. at specific moments (when it

is 'safe').

synonyms: synonyms:

- buffered register - active register

- preload register

- shadow register (?)

There are several terms for both REGX_BUF and REGX from the figure above.

- Usually register

REGXis called the "active register". - Register

REGX_BUFis sometimes called the "buffered register". Other terms are the "preload register" and the "shadow register (?)".

The confusion explained.

Unfortunately there is a confusion about the term "shadow register". From what I read on several sources from the internet, it refers to REGX_BUF. But in the reference manual RM0385 from the STM32F746 microcontroller and RM0410 from the STM32F767 microcontroller I stumble on the exact opposite interpretation of this term "shadow register". It would not refer to REGX_BUF, but rather to REGX.

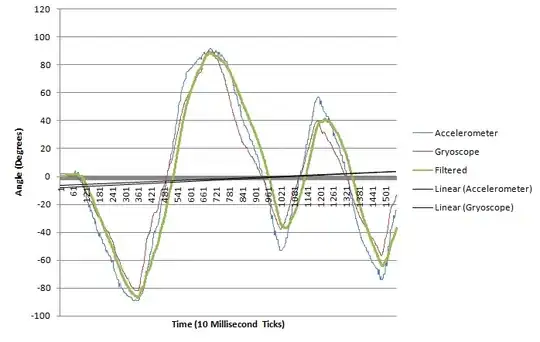

This is a picture from the reference manual:

RM0385 -> chapter 23 General-purpose timers -> 23.3.2 Counter modes -> Fig 199

or

RM0410 -> Chapter 26 General-purpose timers -> 26.3.2 Counter modes -> Fig 244

This figure confuses me. Do I have a wrong interpretation of the term "shadow register", or is it STMicroelectronics who made an error while writing this reference manual?