Unibus (DEC)

Unibus was de eerste van verschillende computerbus- en backplane-ontwerpen van Digital Equipment Corporation (DEC) die gebruikt werden in PDP-11- en vroege VAX-systemen. De Unibus werd rond 1969 ontwikkeld door Gordon Bell en student Harold McFarland tijdens hun studie aan de Carnegie Mellon University.[1]

De naam verwijst naar de uniforme aard van de bus: Unibus werd gebruikt als een systeembus waarmee de centrale verwerkingseenheid kon communiceren met het hoofdgeheugen, en als een perifere bus waarmee randapparatuur gegevens kon verzenden en ontvangen. Door deze voorheen afzonderlijke bussen te combineren, konden externe apparaten direct memory access (DMA) gebruiken en werd de constructie van stuurprogramma's eenvoudiger, omdat de besturing en gegevensuitwisseling allemaal werden afgehandeld via memory-mapped I/O.[2]

Unibus nam fysiek veel plaats in, wat leidde tot de introductie van Q-bus, die sommige signalen multiplexte om het aantal pinnen te verminderen. PDP-systemen met hogere prestaties gebruikten Fastbus, in feite twee Unibussen in één. Het systeem werd later vervangen door Massbus, een speciale I/O-bus die werd geïntroduceerd op de VAX en latere PDP-11-modellen.

Ontwerp

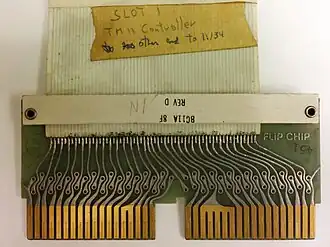

De Unibus bestaat uit 72 signalen, meestal verbonden via twee 36-polige connectoren op elke printplaat. Als de stroom- en aardingslijnen niet worden meegerekend, wordt het meestal een 56-lijnsbus genoemd. Unibus-verbindingen kunnen geïntegreerd zijn in een backplane of kunnen via een kabel tot stand gebracht worden. Er kunnen maximaal 20 knooppunten (apparaten) worden aangesloten op een enkel Unibus-segment. Extra segmenten kunnen worden aangesloten via een busrepeater.

De bus is volledig asynchroon, waardoor een mix van snelle en langzame apparaten mogelijk is. Unibus staat overlapping van arbitrage toe: de selectie van de volgende busmaster kan gebeuren terwijl de huidige busmaster nog steeds gegevensoverdrachten uitvoert. De 18 adreslijnen maken de adressering van maximaal 256 kB mogelijk. Meestal zijn de bovenste 8 kB gereserveerd voor de registers van de memory-mapped I/O-apparaten die worden gebruikt in de PDP-11-architectuur.

Het ontwerp minimaliseert opzettelijk de hoeveelheid redundante logica die nodig is in het systeem. Een systeem bevat bijvoorbeeld altijd meer slave-apparaten dan master-apparaten, dus het grootste deel van de complexe logica die nodig is om asynchrone gegevensoverdrachten te implementeren, bevindt zich noodgedwongen in de relatief weinige master-apparaten. Voor interrupts hoeft alleen de interrupt-fielding processor de complexe timinglogica te bevatten. Het resultaat is dat de meeste I/O-controllers kunnen worden geïmplementeerd met eenvoudige logica en het grootste deel van de kritische logica wordt geïmplementeerd als een aangepaste MSI IC.

Externe link

- (en) Unibus Design Description

(1979) op de website van Bitsavers

(1979) op de website van Bitsavers

Dit artikel of een eerdere versie ervan is een (gedeeltelijke) vertaling van het artikel Unibus op de Engelstalige Wikipedia, dat onder de licentie Creative Commons Naamsvermelding/Gelijk delen valt. Zie de bewerkingsgeschiedenis aldaar.

- ↑ (en) Gardner Hendrie, Bell (Gordon) Oral History. Computer History Museum (23 juni 2005).

- ↑ (en) PDP-11 Buses. University of Sydney. Gearchiveerd op 16 februari 2020.